The ‘Marvellous’ Opening of the AI Accelerator in the 5G RAN

In end-February 2024, Marvell captured large bits of popular imagination when it open sourced OCTEON 10 ML/AI Accelerator Software to what it termed as optimization of 5G RAN Networks. Lying as it does at the intersection of AI and RAN, it is worth taking a deep dive into this development as AI in RAN remains an area of continued focus for Insight Research.

It is worth noting that Marvell’s entry into the 5G domain was a result of the widely reported misfiring of Intel’s 10 nm promise to Nokia and Nokia’s subsequent unsuccessful tryst with Xilinx FPGA. That was 2019 and that was custom Silicon. This is of course, 2024; and we are taking about open-source accelerators. How did we get here?

With a history of close to three decades, Marvell’s tryst with telecommunications is not new. Apart from in-house development, Marvell has over the years acquired companies engaged in ethernet switches, embedded networking software, 3G SoCs, IMS software, network processors and data center switches among others. The acquisition of particular consequence is undoubtedly that of Cavium in 2008. Cavium opened the doors of ARM processor design to Marvell. Arm Neoverse CPUs now adorn the OCTEON 10 processors.

As is well known, OCTEON Data Processing Units (DPU) is the flagship product of Marvell. The so-called infrastructure processors, targeted at 5G applications and sold under OCTEON Fusion and OCTEON TX2 have been successfully used in 5G infrastructure by the Nokia, Samsung and Fujitsu. OCTEON Fusion, for example, is a baseband processor used by Fujitsu in its 5G base stations. Of course, in 2019, Marvell like many other peers were compelled to discontinue shipments to Huawei.

Back to OCTEON 10 baseband DPU. It is Marvell’s first foray 5nm technology for baseband processing, giving greater play for AI and ML use-cases. It also features inline 5G accelerators. Marvell offers these accelerators in PCIe card format and offer in-line L1 acceleration. Marvel is thus positioning itself as a provider of better Open RAN processing options than conventional CPUs. It is here that its path can be thought of intersecting with Nvidia, which also offers ‘options’ to general purpose CPUs. There is a significant difference however. Nvidia’s “AI on 5G” looks at using its GPUs’ excess capacity for Cloud RAN in addition to edge computing applications. Nvidia’s approach and role in the RAN stack is markedly different, and as of date, data-center centric. This may change in future, but we go by what it is today.

The distinction between the approaches of Marvell and Nvidia is important, as Marvell’s stock tends to bask in the “reflected glory” of Nvidia as has been witnessed by the concurrent stock rallies of both the companies in May 2023.

Back to OCTEON 10 baseband DPU again. The announcement of opening these inline accelerators to the Linux Foundation’s DPDK project through the Machine Learning Device Library (MLDEV) route has noteworthy portends. It will now be possible for developers to build ML models on these acceleration engines. This development catapults Marvell into the heart of the Open RAN movement, wherein it can now work with a steadily growing community of RIC vendors, xApp and rApp developers and of course, RAN OEMs.

This development lets loose a plethora of questions:

…and then, how would Ericsson look at this development?

These are million-dollar (or more correctly, several billion-dollar) questions. There are some answers that are immediately apparent, others not so much. We will try and answer a few in subsequent editions. What do you think? Would you like to chip in with your answers? Feel free to share.

|

RELATED BLOGS

Are CNFs, VNFs?

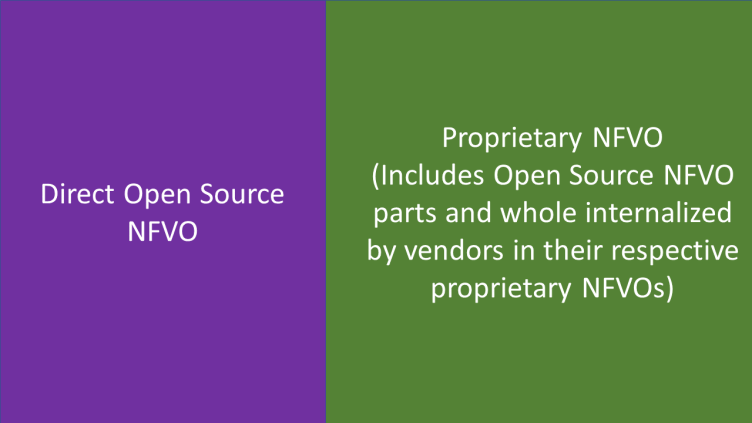

The NFVO Product and its Profiles